# "Instruction Memoization: Exploiting Previously Performed Calculations to Enhance Performance"

A dissertation submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

by

# **Daniel Citron**

Submitted to the senate of the Hebrew University in the year 2000

# "Instruction Memoization: Exploiting Previously Performed Calculations to Enhance Performance"

A dissertation submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

by

# **Daniel Citron**

Submitted to the senate of the Hebrew University in the year 2000

This dissertation was compiled under the supervision of Dr. Dror G. Feitelson.

## Abstract

This thesis explores the concept named memoization: saving the input(s) and output(s) of previously calculated (side-effect-free) functions, and using the output if the input is encountered again. Our focus will be on the memoization of instructions. The operands and results of previous invocations of multi-cycle instructions are saved in dedicated tables named MEMO-TABLES. Successful lookups in these tables, before or parallel to instruction execution, make it possible to improve execution by reducing the latencies of these instructions to one cycle. We named this technique Instruction Memoization (IM).

To test this idea we used a detailed RISC processor simulator running the SPEC and MediaBench benchmarks. We first explore the organization of the MEMO-TABLES in search for an "optimal" design that will maximize hit-ratio and minimize cost. A hit-ratio of over 50% is achieved for moderate sized tables.

Next we integrated IM into a RISC super-scalar processor's datapath. We discovered that 13% of the benchmarks' execution time can be attributed to multi-cycle instructions. With a 52% hit-ratio an average (harmonic mean) speedup of 1.07 was obtained (1.10 for FP intensive applications). In our search for greater performance improvement we decided to memoize single-cycle instructions as well.

The speedup rised by 50% to 1.11 (1.13 for FP applications). However the new speedup is attributed not to instruction latency reduction but rather to the artificial addition of more Functional Units (FUs). The MEMO-TABLES act as "virtual" FUs. Adding more FUs to a processor nullifies the effect of single-cycle IM. On the other hand multi-cycle IM yields a better speedup for faster processors.

# Contents

| 1        | Intr | oduction 1                                                                                                                                                             |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | What is Memoization?                                                                                                                                                   |

|          | 1.2  | Instruction Memoization                                                                                                                                                |

|          | 1.3  | Prior and Related Work                                                                                                                                                 |

|          |      | 1.3.1 Early Use of Memoization                                                                                                                                         |

|          |      | 1.3.2 Instruction Reuse $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4$                                                                             |

|          |      | 1.3.3 Other Techniques                                                                                                                                                 |

|          | 1.4  | Thesis Outline                                                                                                                                                         |

| <b>2</b> | Inst | ruction Memoization 5                                                                                                                                                  |

|          | 2.1  | The Memo-Table                                                                                                                                                         |

|          | 2.2  | The Rationale Behind Instruction Memoization                                                                                                                           |

| 3        | The  | Organization of the Lookup Tables 10                                                                                                                                   |

|          | 3.1  | Simulation Framework                                                                                                                                                   |

|          |      | 3.1.1 Simulations                                                                                                                                                      |

|          |      | $3.1.2  Benchmarks \ldots 11$                                                             |

|          |      | 3.1.3 The Instructions Memoized $\ldots \ldots \ldots$ |

|          | 3.2  | MEMO-TABLE Structural Factors                                                                                                                                          |

|          | 3.3  | Size and Associativity                                                                                                                                                 |

|          | 3.4  | Trivial Calculations                                                                                                                                                   |

|          | 3.5  | Contents of MEMO-TABLES 19                                                                                                                                             |

|          |      | 3.5.1 Exploiting Inverse and Commutative Operations 23                                                                                                                 |

|          | 3.6  | Mapping Strategies                                                                                                                                                     |

|          | 3.7  | Summary 26                                                                                                                                                             |

| 4        | Inte | grating IM in a Processor's Datapath 28                                                                                                                                |

|          | 4.1  | A Basic Microprocessor Design                                                                                                                                          |

|          |      | 4.1.1 Pipeline Stages                                                                                                                                                  |

|          |      | 4.1.2 Functional Units                                                                                                                                                 |

|          |      | 4.1.3 Processor Characteristics                                                                                                                                        |

|          |      | 4.1.4 Integrating IM                                                                                                                                                   |

|          | 4.2  | Basic Processor Speedup                                                                                                                                                |

|          | 4.3  | Measuring Attributes of the Datapath 35                                                                                                                                |

|   |     | 4.3.1 Hit-Ratio                                        | 37        |

|---|-----|--------------------------------------------------------|-----------|

|   |     | 4.3.2 Instructions Per Cycle (IPC)                     | 38        |

|   |     | 4.3.3 Fraction Enhanced (FE)                           | 39        |

|   |     | 4.3.4 Speedup                                          | 39        |

|   |     | 4.3.5 Correlation Between Measurements                 | 40        |

|   | 4.4 | Additional Measurements                                | 41        |

|   |     | 4.4.1 Speedup as a Function of MEMO-TABLE Organization | 43        |

|   | 4.5 | Summary                                                | 43        |

| 5 | Me  | moizing Single Cycle Instructions                      | 45        |

| Ŭ | 5.1 | Comparing Single and Multi-Cycle IM                    | 45        |

|   | 0.1 | 5.1.1 scIM Compared to Other Enhancements              | 47        |

|   | 5.2 | Lowering the cost of scIM                              | 48        |

|   | 0.2 |                                                        | 10        |

| 6 | Cor | nparing IM to Other Techniques                         | <b>50</b> |

|   | 6.1 | Early Memoization                                      | 50        |

|   | 6.2 | Value Prediction                                       | 51        |

|   | 6.3 | Comparing IM to IR                                     | 52        |

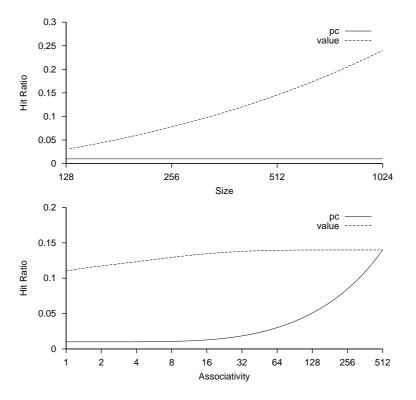

|   |     | 6.3.1 PC vs. Value Mapping                             | 53        |

|   |     | 6.3.2 Table Organization                               | 54        |

|   |     | 6.3.3 Lookup Stage                                     | 55        |

|   |     | 6.3.4 Design Simplicity                                | 55        |

| 7 | Sun | nmary and Conclusions                                  | <b>56</b> |

|   | 7.1 | Memo-Table Organization                                | 57        |

|   | 7.2 | IM in the datapath                                     | 58        |

|   | 7.3 | Single-Cycle Instruction Memoization (scIM)            | 58        |

|   | 7.4 | The Bottom Line                                        | 59        |

| Α | IM  | on Real Processors                                     | 60        |

| _ |     |                                                        |           |

| в |     | moization of Functions                                 | 63        |

|   | B.1 | Memoization of Mathematical Functions                  | 65        |

|   |     | B.1.1 Memoization of Software Implemented Functions    | 65        |

|   |     | B.1.2 Overhead Considerations                          | 67        |

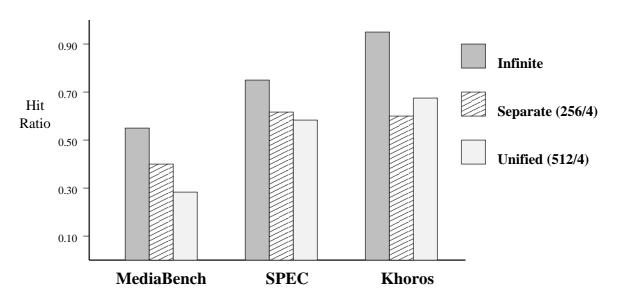

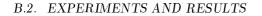

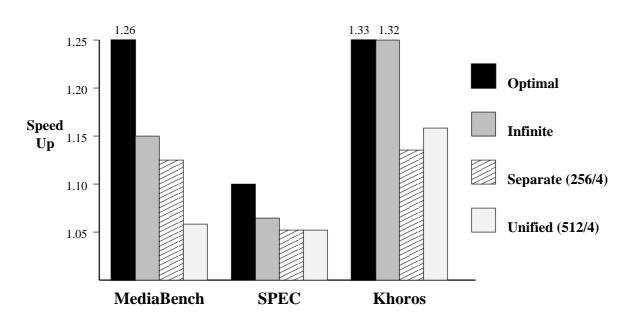

|   | B.2 | Experiments and Results                                | 67        |

|   |     | B.2.1 Simulations                                      | 68        |

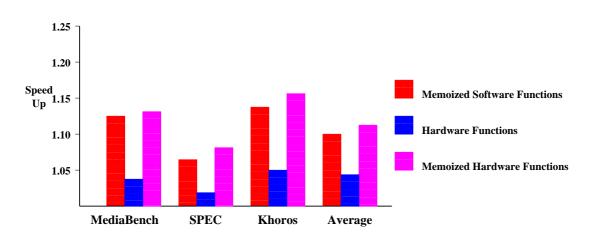

|   |     | B.2.2 Speedups Obtained                                | 69        |

|   |     | B.2.3 Memo-Table Configuration                         | 70        |

|   |     | B.2.4 Memoization of User Functions                    | 72        |

|   |     | B.2.5 Memoization of Functions and Instructions        | 73        |

|   |     | B.2.6 Implementing the Functions in Hardware           | 74        |

|   | B.3 | The Rationale Behind Function Memoization              | 75        |

|   | B.4 | Related Work                                           | 76        |

|   |     | B.4.1 Compiler-Directed Dynamic Computation Reuse      | 77        |

|   |     | B.4.2 Value Profiling                                  | 78        |

|   |     |                                                        |           |

| B.5 | Comparing Hardware to Software Memoization | 78 |

|-----|--------------------------------------------|----|

| B.6 | Summary                                    | 80 |

| 37 | 1 |

|----|---|

| v  | r |

# Chapter 1

# Introduction

In the field of Computer Architecture the end goal of almost all innovations and enhancements is speed. We want our programs to run in less time. This can be achieved in numerous and various ways: running the processor at higher speeds, introducing changes to the design of the processor, changing the instruction set, compiler enhancements, and finally by altering the programs themselves.

This thesis will focus mainly on enhancing the design of the *datapath*. the datapath is by analogy the "blood system" of the processor. Through its stages flow the instructions fetched from memory. The instructions are decoded, their operands are obtained, they are executed, the results of the instructions are written back to memory or the register file, and finally the instructions are committed and exit the datapath. During each cycle, a tick of the processor's clock, instructions either flow through the datapath or are delayed in the datapath until previous instructions have progressed through the stages.

The less cycles it takes instructions to traverse the datapath the faster the program will execute. This thesis shows a technique that shortens the stay of some of the instructons in the datapath. Just as memory caching exploits the "Principal of Locality" in order to present the processor with a short and almost uniform memory access time, we will exploit the concept of *memoization* in order to shorten the execution time of many long latency instructions.

### 1.1 What is Memoization?

The concept of memoization is as follows: saving the input(s) and output(s) of previously calculated (side-effect-free) functions, and using the output if the input is encountered again.

Before a side-effect-free function is to be computed its input(s) are used to access (usually with a hash function) a Look Up Table (LUT). If the inputs are resident in the LUT the previously calculated output(s) is obtained from the table and recalculation of the function is averted. If the input(s) aren't in the LUT the function is calculated and its input(s) and output(s) are stored in the

#### CHAPTER 1. INTRODUCTION

LUT for future reference.

This technique can result in faster recalculations if the storage and lookup of formerly calculated functions is faster then recalculating the function again. But in the general case the LUT is a software based table residing in main memory. Thus the lookup and storage are time consuming. A successful lookup must have a lower access time than calculating the function. Every unsuccessful lookup results in a penalty. Thus a high successful lookup ratio is necessary in order to benefit from memoization. Coupled with the fact that most software based functions aren't side-effect-free, the use of memoization seems limited.

But when looking "right under your code", we find that almost all instructions are side-effect-free (except for memory accesses). And if the LUTs are dedicated tables located on-chip the lookup and storage times are now very short. Thus memoizing instructions seems a much better prospect than memoizing functions. This technique is named *Instruction Memoization (IM)* and is the topic of this thesis.

## **1.2** Instruction Memoization

Instruction Memoization (IM) is a technique that shows great potential for increasing processor performance. The technique exploits the redundancy of instruction results by storing the operands and results of executed instructions in a Lookup Table (LUT), which we will call a MEMO-TABLE. When the same instruction type with matching operands is encountered again the result is obtained from the MEMO-TABLE and instruction execution is avoided. The "execution time" of the instruction is the access time of the MEMO-TABLE, which is a single machine cycle for a small hardware based table. When the lookup is unsuccessful the instruction must be executed in one to tens of cycles (depending on the instruction type). Thus for successful lookups the execution time of these instructions is one cycle, which in turn minimizes their occupancy in the datapath which leads to shorter execution times.

The performance improvement (speedup) obtained is dependent on four major factors:

- 1. The percentage of instructions that can benefit from memoization. Instructions that have a *latency* (number of cycles from execution start until the result is ready) of a single-cycle and instructions that must be executed (stores to memory) are examples of instructions that aren't candidates for memoization. This factor is decided by the application's instruction mix and by the implementation of the microprocessor (latencies of instructions).

- 2. The integration of MEMO-TABLES in the datapath of the processor: The stage of the pipeline that MEMO-TABLES are accessed, multiple-issue of instructions, long-latency instructions completing sooner than expected, and the penalty of an unsuccessful lookup. All these issues affect the usefulness of IM.

#### 1.3. PRIOR AND RELATED WORK

- 3. The percentage of successful lookups, i.e. the hit-ratio of the MEMO-TABLE. This is influenced by the nature of the program being executed, how much redundancy it contains, and by the design of the MEMO-TABLE.

- 4. The physical integration of IM modules on the processor: The number of transistors needed to implement IM, the added power consumption, and the complexity of design all influence the Cost/Performance ratio of implementing IM. This thesis is an architectural research, the physical aspects of implementation are beyond the scope of this work. However the issues will be addressed, tradeoffs compared (not always quantitatively), and solutions given for the problems.

In this thesis we will explore all four factors in order to understand the impact of memoization on the processor and in order to obtain the best possible performance enhancement when using IM.

## **1.3** Prior and Related Work

This section will survey prior and closely related work. At this point in the thesis we won't compare our technique to these works but just present them as is. In chapter 6 after the technique of IM has been fully presented we will compare it to several of the alternate and complementing approaches of reusing previous computations.

#### 1.3.1 Early Use of Memoization

The concept of *memoing* was introduced by Michie [1] in 1968. The idea is to save the inputs and results of side-effect-free functions in a table and reuse the results for matching inputs. Since then it has been used mainly in the context of declarative languages like Prolog, Lisp, and ML [2, 3, 4].

In 1982 Harbison [5] proposed a stack-oriented architecture called the *Tree Machine* (TM) which assumes the role of an optimizing compiler by detecting and eliminating common subexpressions (CSEs) and invariant expressions in loops. It performs this by using a *value cache*. Results of instructions are saved in the value cache. If the same instruction is to be executed and its operands haven't been changed, the result is obtained from the value cache instead of being performed again. Thus the scope of optimizations can be widened to expressions that aren't available at compile time.

The idea of exploiting redundant computation for off-the-shelf RISC architectures was introduced by Richardson [6] in 1992. The results of multiplication, division, and square-root instructions are saved in dedicated tables. When the instructions are to be executed a lookup in the table is performed and if the lookup is successful the result is obtained from the table (this is in fact memoization). This idea was further expanded by Flynn and Oberman [7] (1995) to include storing the reciprocals of division instructions.

#### CHAPTER 1. INTRODUCTION

#### 1.3.2 Instruction Reuse

In 1997 Sodani & Sohi [8] introduced the concept of *Instruction Reuse (IR)*. All instructions, even single-cycle instructions are candidates for reuse. The instructions are inserted in a table called the *Reuse Buffer (RB)*. Instructions in the RB are accessed using the Program Counter (PC). If the operand values of the instruction match the operands values in the RB, the result is obtained from the the RB. Variations of the scheme include matching the operand register names (requires invalidation of entries if the registers were written into), and matching instructions that supply the current instruction with its operands (again requires invalidation). The technique of IR is closely related to IM and in some cases overlaps it. In chapter 6 we will describe the differences in detail.

#### 1.3.3 Other Techniques

Other techniques such as Value Prediction (VP) (Gabbay & Mendelson [9], Lipasti, Wilkerson & Shen [10, 11], and Sazeides & Smith [12]), Compiler-Directed Dynamic Computation Reuse (Connors and Hwu [13]), and Value Profiling (Calder, Feller & Eustace [14]) will be presented in more detail in chapter 6.

### 1.4 Thesis Outline

The rest of this thesis covers the following topics: Chapter 2 describes how IM works and shows the rationale behind its success. Chapter 3 explores various organizations of the MEMO-TABLE. Chapter 4 describes the integration of IM into the processor's datapath. Chapter 5 shows how single-cycle instructions can use IM. Chapter 6 compares IM to other similar research efforts and chapter 7 concludes this thesis. Two appendices at the end of the thesis show how IM performs on real world processors (appendix A) and appendix B widens the scope of IM to include function memoization.

# Chapter 2

# Instruction Memoization

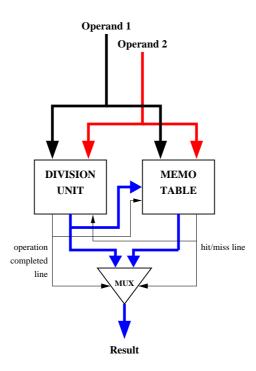

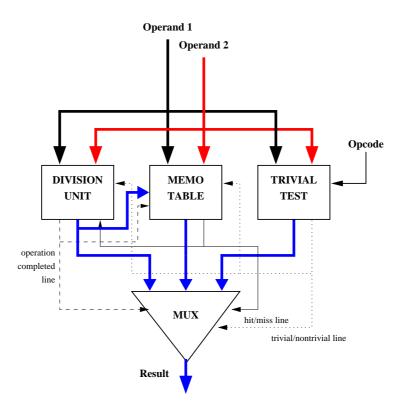

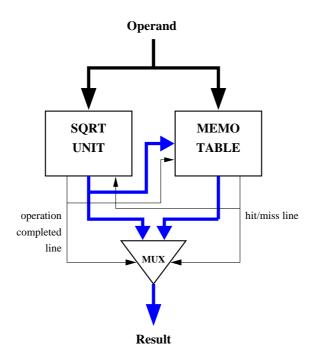

In this chapter we will describe in detail how Instruction Memoization (IM) works and the basic structure of the MEMO-TABLE. The idea is to mitigate the effect of *multi-cycle* instructions (instructions with a latency of more than one cycle) by reducing their latency via IM. The input (operands) and output (result) of particular instruction types are stored in a cache-like lookup table (the MEMO-TABLE). The MEMO-TABLE is accessed in parallel to the conventional computation. A successful lookup gives the result of a multi-cycle computation in a single cycle, and a failed lookup doesn't necessitate a penalty in computation time. Figure 2.1 shows a schematic layout of the idea. The operands are forwarded in parallel both to a division unit and its adjacent MEMO-TABLE.

### 2.1 The MEMO-TABLE

A MEMO-TABLE is a cache-like Look Up Table (LUT), that is placed adjacent to each Functional Unit (FU) that has a latency of multiple cycles. The likeness to a cache is due to the fact that the values in the LUT change dynamically over time with the most recently used values present in the MEMO-TABLE.

Just like in a conventional cache when a value is forwarded to the MEMO-TABLE, a subset of its bits are used to form an index into the LUT. The remaining bits are compared to the value stored in the indexed entry. If they match, we say that we have a "hit" and the value stored in the entry is returned. If they do not match, we say that we have a "miss", no value is returned and the table is updated with a new value (evicting an "older" entry). Which subset of bits to use is one of the characteristics explored in section 3.6.

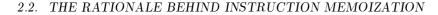

Unlike a conventional cache where each line contains more than one word and a relatively small associated tag, the MEMO-TABLE contains a large tag and just the one word result in each line. To emphasize this distinction, we shall use *entry* instead of the traditional *line* or *block*. Figure 2.2 shows a MEMO-TABLE with n entries. The shaded area contains the results, the unshaded areas contains the operands and opcode (in the case where several instruction types

#### CHAPTER 2. INSTRUCTION MEMOIZATION

Figure 2.1: A division unit using a MEMO-TABLE

reside in the same MEMO-TABLE) which are compared to the operands and opcode of the instruction being memoized. Note that no valid bit is necessary, and data is valid at all times even across context switches due to the fact that the instructions stored in MEMO-TABLES are context free, the result depends only on the operands<sup>1</sup>. The only time invalid data is in a MEMO-TABLE is during startup, initially loading the opcode fields with invalid opcode solves this problem.

During execution the operands are forwarded to the appropriate computation unit and in parallel, to the corresponding MEMO-TABLE. If there is a hit in the MEMO-TABLE, its value is forwarded to the next pipeline stage , the computation in the FU is aborted and it signals it is free to receive the next set of operands. If there is a miss in the MEMO-TABLE, the computation is allowed to complete, and the result obtained is forwarded to the next stage and in parallel entered into the MEMO-TABLE.

<sup>&</sup>lt;sup>1</sup>Except if different IEEE 754 rounding modes are used.

Figure 2.2: Layout of a *n* entry MEMO-TABLE.

# 2.2 The Rationale Behind Instruction Memoization

After we have shown the basic IM technique we will explain why it should work. To best understand the rationale a few examples will be presented:

- **vsqrt** The application vsqrt takes the square-root of all pixels in an image. We have previously shown [15] that neighboring pixels in an image tend to have the same values, thus leading to a high hit-ratio in the MEMO-TABLE.

- vspatial Performs image enhancement based on local histograms. An examination of a sample image, a self portrait of Guya (figure 2.3), shows that out of 256 possible pixel values only 161 are represented (figure 2.4). Zooming in to an 8x8 window surrounding Guya's nose (figure 2.5) shows that there are only 11 unique values. Building a histogram of this windows and running the following loop:

```

n = N*N; /* N=8 */

for(i=0;i<L;i++) /* L = # of values */

e += (hist[i]/n) * log2(hist[i]/n);</pre>

```

results in a 94% hit-ratio when memoizing division. The same is true for color images which are composed of three "bands" (red, green, and blue images). Each band displays a similar amount of redundancy.

tomcatv In the following code excerpt  $^2$ :

A = 0.25 \* (XY\*XY+YY\*YY)B = 0.25 \* (XX\*XX+YX\*YX)

<sup>&</sup>lt;sup>2</sup>This excerpt was taken from Richardson's paper [6].

#### CHAPTER 2. INSTRUCTION MEMOIZATION

The number of unique pairs is 769. Using an "infinite" multiplication MEMO-TABLE results in an almost perfect hit-ratio.

As we can see the nature of the programs and inputs causes instruction repetition. Most Multi-Media applications work on local areas of an image or signal which may result in the same calculations being performed over and over again. Of course not all programs that exhibit redundancy have source code excerpts that pinpoint the cause, most don't.

Figure 2.3: A self portrait of Guya.

Figure 2.4: Histogram of the Guya image.

Sodani and Sohi [16] have performed a detailed analysis of instruction repetition for the SPEC 95 integer benchmarks and have found that most of the repetition originates from internal values of the program (immediates) or from global initialized data. Our conclusions are that for most Floating Point benchmarks the redundancy originates from the input sets of the applications [15].

## 2.2. THE RATIONALE BEHIND INSTRUCTION MEMOIZATION 9

Figure 2.5: A blowup of Guya's nose.

# Chapter 3

# The Organization of the Lookup Tables

This chapter is dedicated to finding the near optimal design for MEMO-TABLES that will enable us to receive the maximal hit-ratio possible (for finite MEMO-TABLE sizes). In this chapter we memoize all instructions that have a latency of more than one cycle<sup>1</sup>. The MEMO-TABLE we will explore is the same as proposed in chapter 2. Each entry consists of two operands, a result, and an opcode. The organization of the processor's datapath is irrelevant at this stage of the research and will be explored in chapter 4 after we fix the MEMO-TABLE characteristics.

The characteristics of the MEMO-TABLES explored are its cache-like traits: size, associativity, and replacement method, and characteristics that are unique to memoization such as indexing methods (which bits of the values compose the index into the MEMO-TABLE), contents (which instructions are in each MEMO-TABLE), detection of trivial calculations that can be computed easily (x + 0, y \* 1, ...), and the relationships between instructions types  $(a + b = c \rightarrow c = b - a, ...)$ .

### 3.1 Simulation Framework

To find the optimal design of a MEMO-TABLE we performed a series of experiments with an architecturally detailed simulator: SimpleScalar [17], a RISC instruction-level simulator based upon the MIPS ISA. SimpleScalar receives as input a binary executable compiled for the simulator and executes it down to the cycle level. All applications were compiled using gcc version 2.6.3 with the optimization flags -03 -finline-functions -funroll-loops. We tailored SimpleScalar to incorporate MEMO-TABLES in it's design and thus simulate IM.

The two indicators that measure the success of the memoization are:

<sup>&</sup>lt;sup>1</sup>Except memory accesses which aren't side-effect free (stores) or aren't context free (loads).

#### 3.1. SIMULATION FRAMEWORK

- **Hit-Ratio** The hit-ratio of a MEMO-TABLE (number of successful lookups divided by number of lookups) will show how many instruction executions were avoided.

- **Speedup** The end goal of using MEMO-TABLES is to accelerate processing; if the enhancement has no impact on performance, the extra complexity of adding it isn't worth the effort.

The emphasis of the simulations in this chapter will be on enhancing the hitratios of the MEMO-TABLES. The speedup achieved by using IM will be shown in chapter 4.

#### 3.1.1 Simulations

The simulations were performed using the SimpleScalar simulator. As we want to negate the influence of the datapath the programs were run through the sim-fast version of the simulator. This version simulates instruction execution step-by-step but doesn't simulate the memory hierarchy, pipelining, multipleissue, branch prediction, or any other architectural enhancements (except the use of MEMO-TABLES, of course).

#### 3.1.2 Benchmarks

The benchmarks were taken from several sources:

- **SPEC CFP95** the floating point component of the SPEC CPU95 suite [18].

- SPEC CINT95 the integer component of the SPEC CPU95 suite [18].

- MediaBench a suite of multi-media and communication applications from UCLA [19].

The benchmark applications are either FP intensive or perform integer multiplication and/or division. Applications that don't execute large amounts of multiple-latency instructions can't benefit from IM and aren't simulated<sup>2</sup>.

Table 3.1 describes the specific applications, the number of instructions executed, and the percentage of multiple-cycle instructions executed<sup>3</sup>. Even though less than 1% of the instructions in integer intensive applications are multiplecycle instructions we simulate them and give them an equal standing to FP

$<sup>^2</sup>$  For this reason adpcm and pegwit from the MB suite and li and go from CINT95 aren't simulated. Jpeg from MB and ijpeg from CINT95 are similar so only jpeg is run. m88ksim from CINT95 is invariant to any MEMO-TABLE changes, 99% of all integer multiplications are reused in any configuration, thus this application was dropped from the simulations.

<sup>&</sup>lt;sup>3</sup>In some cases the numbers are the sum of several applications that make up a benchmark (eg. decode and encode for mpeg2). The SPEC benchmarks were run with the test or train versions of the inputs in order to keep them relatively short, running them with the reference inputs gives similar results.

| suite      | application | description                    | input                        | # of insts        | %     |

|------------|-------------|--------------------------------|------------------------------|-------------------|-------|

| MediaBench | rasta       | Speech recognition             | ex5_c1.wav                   | 23M               | 10.4% |

|            | mesa        | 3D graphics library            | hardcoded                    | 130M              | 17.8% |

|            | mpeg2       | Video compression              | mei16v2.m2v                  | 1282M             | 7.8%  |

|            | epic        | Image compression              | lenna.pgm                    | 60M               | 15.5% |

|            | gsm         | Speech transcoding             | clinton.pcm                  | 223M              | 14.9% |

|            | ghostscript | Postscript interpreter         | tiger.ps                     | 1294M             | 4.4%  |

|            | g721        | Voice compression              | $\operatorname{clinton.pcm}$ | 529M              | 0.6%  |

|            | pgp         | Cryptography                   | pgptest.pgp                  | $159\mathrm{M}$   | 2.3%  |

|            | jpeg        | Image compression              | monalisa.jpg                 | 161M              | 0.3%  |

| CFP95      | tomcatv     | Vectorized mesh generation     | train.in, ITACT=20           | 818M              | 10.4% |

|            | swim        | Shallow water equations        | train.in                     | 842M              | 26.3% |

|            | su2cor      | Monte-Carlo method             | test.in                      | $1050 \mathrm{M}$ | 12.8% |

|            | hydro2d     | Navier Stokes equations        | test.in                      | 1124M             | 16.4% |

|            | mgrid       | 3D potential field             | train.in, NTIMES=1           | 382M              | 14.5% |

|            | applu       | Partial differential equations | train.in, it max= $20$       | $1000 \mathrm{M}$ | 7.7%  |

|            | turb3d      | Turbulence modeling            | train.in, nsteps=1           | 398M              | 7.5%  |

|            | apsi        | Weather prediction             | test.in                      | 888M              | 22.6% |

|            | fpppp       | Quantum chemistry              | train.in                     | 344M              | 32.8% |

|            | wave5       | Maxwell's equation             | test.in, nsteps=2            | $1389 \mathrm{M}$ | 31.7% |

| CINT95     | gcc         | C compiler                     | $1  \mathrm{stmt.i}$         | 119M              | 0.3%  |

|            | compress    | Lempel-Ziv compression         | test.in                      | 35M               | 0.5%  |

|            | perl        | Perl interpreter               | scrabll.pl, train input      | 40M               | 0.4%  |

Table 3.1: Description of benchmark applications, inputs, number of instructions executed, and percentage of multiple-cycle instructions.

intensive applications<sup>4</sup>. We are exploring primarily MEMO-TABLE characteristics not overall speedup, thus the impact of these applications which have a different instruction mix than FP applications is important. The following simulation results are the average (harmonic mean) hit-ratios of the MEMO-TABLES for all the above applications<sup>5</sup>.

#### 3.1.3 The Instructions Memoized

All the instructions memoized have a latency of more than one cycle. These include integer division and multiplication and all the floating point instructions. Table 3.2 lists the instructions memoized along with their latencies and throughputs<sup>6</sup> on the R10000 and  $604e^7$ . For each instruction type there is a

$<sup>^4\</sup>mathrm{The}$  integer intensive applications are g721, pgp, and jpeg from MediaBench and the CINT benchmarks.

$<sup>^5{\</sup>rm The}$  average is unweighed, every benchmark, short or long running, has an equal standing. We didn't want the SPEC benchmarks, which have a longer execution time, to dominate the results.

$<sup>^{6}\</sup>mathrm{If}$  an unit is pipelined it can complete an instruction every cycle, this is the throughput of the instruction.

<sup>&</sup>lt;sup>7</sup>The 604e doesn't implement the **fsqrt** instruction listed in its instruction set, we decided to do so in our simulator in order to compare the datapaths of both processors (a software

#### 3.2. MEMO-TABLE STRUCTURAL FACTORS

| instruction                        | MIPS R10000 |       | PPC   | 604e  |

|------------------------------------|-------------|-------|-------|-------|

| type                               | lty         | thpt  | lty   | thpt  |

| Int Division                       | 35          | 35    | 20    | 19    |

| Int Multiplication                 | 6           | 6     | 3     | 1     |

| FP Add/Subtract                    | 2           | 1     | 3     | 1     |

| FP Comparison                      | 2           | 1     | 3     | 1     |

| $FP \leftrightarrow FP$ Conversion | 2           | 1     | 3     | 1     |

| $FP \rightarrow Int Conversion$    | 2           | 1     | 3     | 1     |

| $Int \rightarrow FP Conversion$    | 4           | 1     | 3     | 1     |

| FP Neg/Abs                         | 2           | 1     | 3     | 1     |

| FP Move                            | 2           | 1     | 3     | 1     |

| FP Multiplication                  | 2           | 1     | 3     | 1     |

| FP Division (sp/dp)                | 12/19       | 14/21 | 18/31 | 18/31 |

| $FP Sqrt (sp/dp)^*$                | 18/33       | 20/35 | 50/60 | 50/60 |

MEMO-TABLE that stores the operands and results of the instances of the instruction, for a total of 19 such MEMO-TABLES in use.

\* The 604e doesn't implement the fsqrt instruction.

Table 3.2: Instruction latencies and throughputs for the MIPS R10000 and PPC 604e.

## **3.2** Memo-Table Structural Factors

We first measured the effects of four factors related to the structure of the MEMO-TABLE rather than to its contents. The factors and their levels are:

- Size the number of entries in each MEMO-TABLE, the levels are from 8 to 16K entries, and an infinite table size.

- Associativity the number of entries in each set. The levels are from direct-mapped (set size 1), to 8-way set associative (set size 8), and fully associative (one set).

- Replacement Strategy Which entry is evicted from the MEMO-TABLE in the case of a miss. The levels are: replace randomly, First In First Out (FIFO), pseudo Least Recently Used (where the LRU entry is approximated), Most Recently Used (MRU) and true LRU. As memoization isn't speculative we don't explore any confidence schemes, once a value is in the MEMO-TABLE it is valid.

- Mapping Strategy How an entry is mapped to a set. The levels are to hash the Program Counter (like [8] do) or hash the values. The values can be hashed using various techniques, simple ones such as hashing the Least Significant Bits (LSBs), to more complex techniques which hash the exponent, mantissa or some bit mix of them.

implementation of the sqrt function can take over 1000 cycles).

The number of simulations needed to perform a *full factorial design*, simulating every possible combination of all levels, would take:  $n = \prod_{i=1}^{k} n_i$  simulations. In our case it is (12 levels of size)×(5 levels of associativity)×(5 levels of replacement schemes)×(6 levels of mapping strategies) = 1800 simulations for each and every application. This number is daunting and beyond our processing power.

In such cases where a full factorial design is impossible, a  $2^k$  factorial design is used. For each factor two levels or alternatives are chosen resulting in only 16 simulations in our case. These simulations can give us an indication which factors have a higher impact on the hit-ratios and which factors have little or no impact at all.

By using the *Sign-Table* [20] technique it is possible to compute the *allocation* of variation of each factor and the interaction between factors. The importance of a factor is measured by the proportion of the total variation in the result that is explained by the factor.

The levels chosen for simulation are: Size - 32, 1024 entries; Associativity - direct mapped, 8-way set associative; Replacement Strategy - random, LRU; Mapping - PC, value (LSBs); The results (harmonic mean hit-ratios of all applications) are shown in table 3.3.

| 32         | 1           | $\operatorname{rand}$ | $\mathbf{pc}$ | 0.17                                        | 32         | 1           | rand                  | val        | 0.32         |

|------------|-------------|-----------------------|---------------|---------------------------------------------|------------|-------------|-----------------------|------------|--------------|

| 1024       | 1           | $\operatorname{rand}$ | $\mathbf{pc}$ | 0.22                                        | 1024       | 1           | $\operatorname{rand}$ | val        | 0.39         |

| 32         | 8           | $\operatorname{rand}$ | $\mathbf{pc}$ | 0.30                                        | 32         | 8           | $\operatorname{rand}$ | val        | 0.39         |

| 1024       | 8           | $\operatorname{rand}$ | рс            | 0.32                                        | 1024       | 8           | $\operatorname{rand}$ | val        | 0.51         |

|            |             |                       |               |                                             |            |             |                       |            |              |

| 32         | 1           | lru                   | рc            | 0.17                                        | 32         | 1           | lru                   | val        | 0.32         |

| 32<br>1024 | 1           | lru<br>lru            | pc<br>pc      | $\begin{array}{c} 0.17 \\ 0.22 \end{array}$ | 32<br>1024 | 1<br>1      | lru<br>lru            | val<br>val | 0.32<br>0.39 |

| -          | 1<br>1<br>8 |                       | -             |                                             | -          | 1<br>1<br>8 |                       |            |              |

Table 3.3:  $2^4$  factorial design and resulting hit-ratios. The factors and levels are size (32, 1024), associativity (direct mapped, 8-way set associativity), replacement strategy (random, lru) and the hashing scheme (pc, value).

The results obtained are inserted into a Sign-Table. The sample variance of the data is calculated by computing the Sum of Squares Total (SST), this number can then be broken into its components. The main components of variation are: Mapping scheme - 55%, Associativity - 31%, and Size - 10%. The variation attributed to the replacement strategy is 0%. From these numbers and a look at the table we can make two important observations:

- 1. The mapping scheme is of utmost importance. The left hand side of the table which uses the PC as the index into the MEMO-TABLES shows consistently poorer results than the right hand side which uses the operand values as indices into the MEMO-TABLES. Thus in future simulations we will use the operand values only as indices. Section 3.6 explains this phenomena in greater detail.

- 2. The replacement strategy is of little importance. The top half of the table

#### 3.3. SIZE AND ASSOCIATIVITY

which uses a random replacement strategy has the same results as the bottom half which uses the LRU replacement strategy. This is consistent with memory caches where the replacement method has little impact on the hit-ratio [21]. The reason is that values that are highly reused will be reentered into the MEMO-TABLE, even if they were randomly evicted. Because of the simplicity of implementing a random replacement method we use this method in future simulations.

15

The variation allocated to size and associativity and the results displayed prohibit us from making clean cut decisions as with the mapping and replacement method. We must investigate more levels of both size and associativity, we will do this in the next section.

## 3.3 Size and Associativity

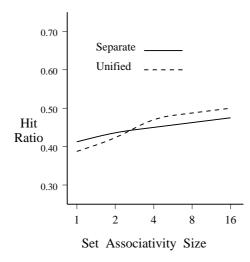

The next set of simulations are targeted at determining the highest hit-ratio with the lowest MEMO-TABLE size and associativity. The levels of size are from 16 to 16K entries per MEMO-TABLE (omitting 512, 2K, and 8K sizes) and an infinitely large MEMO-TABLE (1MB entries), and the levels of associativity are from direct-mapped to 8-way set associative and fully associative (for large MEMO-TABLEs an associativity of 512 was used).

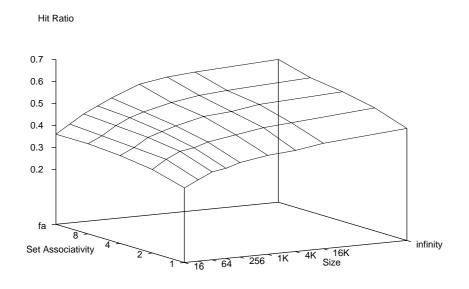

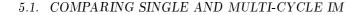

Figure 3.1: Hit-ratio as a factor of MEMO-TABLE size and set associativity.

A two-factor full factorial design is used [20] to determine which factor influences the hit-ratio more. The total variation can be divided into parts explained by factors A (size) and B (associativity) and an unexplained part due to experimental errors. The results show that 68% of the variation is attributed to changes in the MEMO-TABLES size and 30% to changes in the associativity, 2% of the variation is unexplained.

| Size/Assoc | 1    | 2    | 4    | 8    | full |

|------------|------|------|------|------|------|

| 16         | 0.29 | 0.33 | 0.35 | 0.36 | 0.36 |

| 32         | 0.32 | 0.37 | 0.38 | 0.39 | 0.40 |

| 64         | 0.35 | 0.40 | 0.42 | 0.43 | 0.44 |

| 128        | 0.36 | 0.41 | 0.44 | 0.46 | 0.47 |

| 256        | 0.38 | 0.43 | 0.46 | 0.48 | 0.50 |

| 1 <i>K</i> | 0.40 | 0.45 | 0.49 | 0.51 | 0.55 |

| 4K         | 0.41 | 0.47 | 0.50 | 0.53 | 0.57 |

| 16K        | 0.43 | 0.48 | 0.52 | 0.54 | 0.58 |

| infinite   | 0.46 | 0.51 | 0.54 | 0.56 | 0.60 |

Table 3.4: Tabular version of hit-ratio as a factor of MEMO-TABLE size and set associativity.

Figure 3.1 is a 3-D plot of the hit-ratio (z-axis) as a function of size (x-axis), and associativity (y-axis) (the actual results are in table 3.4). Looking at the lesser factor of variation, associativity, shows that raising the associativity from direct-mapped to 2-way gives a considerable hit-ratio enhancement and raising the associativity beyond 4-way hardly changes the hit-ratio. This is fortunate as implementing a 8-way set associative MEMO-TABLE is the cutting-edge [22] of current on-chip memory cache technology which will be used in implementing MEMO-TABLES. Current on-chip caches can perform a 4-way set associative cache lookup in a single machine cycle so there is no reason not to set the associativity of MEMO-TABLES to 4.

Looking at the plot again shows that for sizes 16 to 128 the curve rises rapidly, from MEMO-TABLE size 256 the curve starts to flatten. Dividing the hit-ratio of using 256 entry 4-way set associative MEMO-TABLES with the hit-ratio of using infinite fully-associative MEMO-TABLES, shows that 76% of all reusable multiple-cycle instructions can be reused with moderate size MEMO-TABLES.

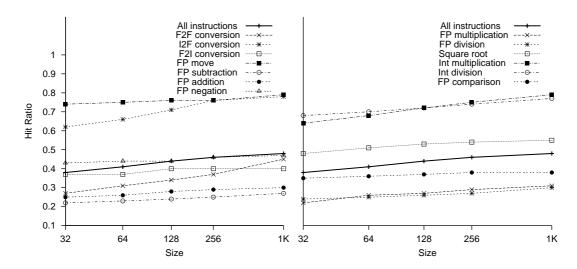

Figure 3.2 shows the breakdown of hit-ratios per instruction (associativity: 4; size: 32-1024). It is noticeable that the hit-ratios for the integer instructions are amongst the highest and they continue to benefit from a larger MEMO-TABLE after the hit-ratios for other instructions flatten out (as does single precision to double precision conversion). For the square-root, FP comparison, and FP  $\leftrightarrow$ INT conversion instructions the hit-ratio is invariant to MEMO-TABLE sizes above 128 entries. For FP move a MEMO-TABLE of size 64 is sufficient. Nevertheless, in order to work with a uniform MEMO-TABLE size we will use a baseline size of 256 in future simulations.

Another consideration to take into account is the *hit-time* (the time to

Figure 3.2: Breakdown of hit-ratio by instruction type (4-way set associativity, random replacement, mapping by value).

access a MEMO-TABLE, check if the entry is resident in the MEMO-TABLE, and return the result) of a MEMO-TABLE. This time must be a single machine cycle, with most FP instructions having latencies of 2-3 cycles, a longer hit-time will reduce the effectiveness of IM. Thus the size of a MEMO-TABLE should be comparable to the size of small on-chip caches, which have a hit-time of one cycle. A 256 entry MEMO-TABLE holds  $256 \times 3 = 768$  double precision values which is  $768 \times 8 = 6144 = 6K$  bytes. This is considerably less than the on-chip caches of the MIPS R10000 (32KB), Power PC 604e (32KB) and other leading microprocessors. Thus in any case the upper limit on the size of MEMO-TABLES will be 1024 entries (24KBytes) with a set associativity of 4.

## 3.4 Trivial Calculations

The result of a trivial calculation is immediately obtained from the operands of the calculation itself. No calculation is performed, just a input check is needed to detect the occurrence of triviality. In all previous simulations trivial calculations were treated as regular calculations and forwarded to the MEMO-TABLES. In this section trivial calculations will be detected in parallel to the MEMO-TABLES. Table 3.5 shows the trivial calculations detected. Figure 3.3 shows the layout of a MEMO-TABLE, division unit, and trivial test unit. The calculation is tested for triviality in parallel to the MEMO-TABLE lookup and FU execution. If the calculation is trivial the result will be obtained from the Trivial Test Unit (TTU), and the MEMO-TABLE lookup and FU execution will be terminated. If

| Addition              | a + 0, 0 + a             | a   |

|-----------------------|--------------------------|-----|

| Subtraction           | a-0                      | a   |

|                       | a - a                    | 0   |

| Multiplication        | $a \times 0, 0 \times a$ | 0   |

|                       | $a \times 1, 1 \times a$ | a   |

| Division              | a/1                      | a   |

|                       | 0/a                      | 0   |

|                       | a/0                      | Inf |

|                       | 0/0                      | NaN |

|                       | a/a                      | 1   |

| $\operatorname{Sqrt}$ | $\sqrt{1}$               | 1   |

|                       | $\sqrt{0}$               | 0   |

|                       | a < 0                    | NaN |

| Conversions           | 0                        | 0   |

| Negation              | 0                        | 0   |

| Absolute Value        | 0                        | 0   |

Table 3.5: Operation, trivial calculation, and result.

the calculation isn't trivial the MEMO-TABLE lookup or FU execution supplies the result (for clarity each control line is drawn using a different line style).

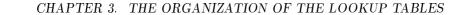

The TTU is composed of a set of 4 comparators, a FP negative bit test, and combinational logic to detect triviality (figure 3.4). This design covers all the triviality tests defined in table 3.5 and enables building a uniform  $TTU^8$ .

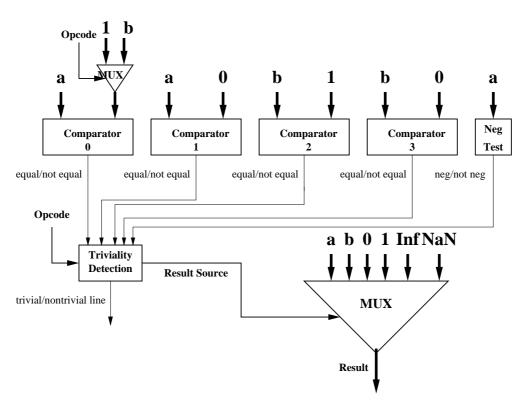

Table 3.6 shows the hit-ratios for 256 entry (4-way sets) MEMO-TABLES with and without trivial calculation detection, and the percentage of trivial calculations out of all memoized instructions. An average 3% enhancement is possible by just adding circuits to perform trivial calculation detection, as opposed to quadrupling the MEMO-TABLES size in order to achieve the same enhancement as shown by figure 3.5. For FP applications, MEMO-TABLES of size 128 with trivial calculation detection have higher hit-ratios than 1K entry MEMO-TABLES without trivial calculation detection.

Table 3.7 shows the main trivial operation contributers. For each instruction type: the trivial operation ratio, the percentage out of all trivial instructions, and the breakdown of trivial values detected is displayed. The tables shows that 93% of all trivial instructions contain the values one or zero. Thus we can simplify the triviality check by just testing for zero and one. We can further narrow down the scope of the triviality test by just checking triviality for the top contributers (multiplication, addition, subtraction, and division) but for the sake of uniformity we will check triviality (zero and one only) for all relevant instructions. Thus our conclusions are straightforward: each MEMO-TABLE will have a TTU integrated into it, this achieves a hit-ratio enhancement comparable to a size increase of one order of magnitude.

$<sup>^8 \, {\</sup>rm Just}$  as an integer Memo-Table is different than a FP Memo-Table so is an integer TTU different than a FP TTU.

#### 3.5. CONTENTS OF MEMO-TABLES

Figure 3.3: Layout of a Trivial Test Unit adjacent to a MEMO-TABLE and Division Unit.

# 3.5 Contents of MEMO-TABLES

Our previous simulations used a MEMO-TABLE for each instruction type. It is possible that for different applications some MEMO-TABLES won't be utilized at all, while others will suffer from capacity misses. Microprocessors have separate Instruction and Data caches to make it possible to access them at the same cycle, not because this enhances the hit-ratio (it doesn't [21]). On the other hand one centralized MEMO-TABLE will suffer from a longer hit-time, might have to be multi-ported, might suffer from non-uniform access due to line delays, and disallows different mapping schemes for integer and floating point values.

Our previous simulations show that the average number of MEMO-TABLES used per application is 11.7 (out of 19). When counting the number of accesses per MEMO-TABLE we discovered that the mean is lower than the standard deviation for all applications. This shows that there are many tables that are accessed relatively little and a few which are highly accessed, leading us to assume that using a unified MEMO-TABLE might enhance the hit-ratio.

Due to the problems in using a unified table mentioned earlier we suggest adding a level between MEMO-TABLE per instruction to a unified MEMO-TABLE.

Figure 3.4: Layout of a Trivial Test Unit, the opcode of the instruction determines which comparisons are used.

The motivations for a specific setup are the utilization per table, the functional units that process each instruction, and the effect of the MEMO-TABLES' size on the hit-ratio. Each MEMO-TABLE will contain one heavily executed instruction and one or more under utilized instructions. Thus are choice of tables is:

- 1. Integer integer multiplication (heavily used) and division (lightly used). Both use the same unit (604e) or adjacent units (R10000). This table will be the largest (double size) as the hit-ratio constantly rises for a larger MEMO-TABLE size (section 3.3). Total dynamic instruction count: 35%.

- 2. Long Latency floating point multiplication (heavily used), division, and square root taking. Usually share circuitry in most microprocessors. Total dynamic instruction count: 24%.

- 3. Addition floating point addition. Total dynamic instruction count: 18%.

- 4. Subtraction floating point subtraction (moderately used), negation,

#### 3.5. CONTENTS OF MEMO-TABLES

| application   | org hr | new hr | trivial ratio |

|---------------|--------|--------|---------------|

| mesa          | 0.42   | 0.51   | 23%           |

| epic          | 0.15   | 0.18   | 4%            |

| rasta         | 0.32   | 0.37   | 9%            |

| mpeg2         | 0.58   | 0.65   | 51%           |

| gsm           | 0.05   | 0.08   | 3%            |

| ghostscript   | 0.96   | 0.97   | 57%           |

| jpeg          | 0.82   | 0.84   | 54%           |

| g721          | 0.49   | 0.51   | 22%           |

| pgp           | 0.07   | 0.07   | 0%            |

| tomcatv       | 0.19   | 0.28   | 13%           |

| swim          | 0.19   | 0.22   | 7%            |

| su2cor        | 0.25   | 0.26   | 5%            |

| hydro2d       | 0.90   | 0.93   | 46%           |

| mgrid         | 0.69   | 0.71   | 6%            |

| applu         | 0.40   | 0.43   | 7%            |

| turb3d        | 0.75   | 0.83   | 62%           |

| apsi          | 0.35   | 0.40   | 16%           |

| fpppp         | 0.40   | 0.44   | 8%            |

| wave5         | 0.11   | 0.12   | 1%            |

| gcc           | 0.94   | 0.96   | 72%           |

| compress      | 0.13   | 0.13   | 8%            |

| perl          | 0.96   | 0.97   | 1%            |

| harmonic mean | 0.46   | 0.49   | 22%           |

Table 3.6: Hit-ratios for 256 entry (4 entries to a set) MEMO-TABLES with and without trivial calculation detection, and the percentage of trivial calculations out of all memoized instructions.

| instruction                     | tr/ac | inst/all | value | e brea | kdowi | n (%) |

|---------------------------------|-------|----------|-------|--------|-------|-------|

|                                 |       |          | 0     | 1      | =     | -     |

| Int Multiplication              | 0.38  | 0.31     | 45    | 55     | 0     | 0     |

| FP Multiplication               | 0.23  | 0.25     | 86    | 14     | 0     | 0     |

| FP Addition                     | 0.26  | 0.22     | 100   | 0      |       | 0     |

| FP Subtraction                  | 0.24  | 0.11     | 42    | 0      | 52    | 0     |

| Int Division                    | 0.25  | 0.3      | 46    | 29     | 24    | 0     |

| FP Division                     | 0.13  | 0.2      | 56    | 30     | 14    |       |

| Int $\rightarrow$ FP Conversion | 0.8   | 0.2      | 100   | 0      | 0     | 0     |

| All Instructions                | 0.22  | 1.00     | 72    | 21     | 7     | 0     |

Table 3.7: Breakdown of triviality per instruction type. Column 2 is the trivial ratio out of all MEMO-TABLE accesses, column 3 is the ratio between the instructions' trivial operations to all trivial operations, and the last columns show the breakdown of the trivial values.

absolute value and move. Using MEMO-TABLES both for addition and subtraction, although they use the same circuitry, makes it possible to

22

Figure 3.5: Changes in hit-ratio of MEMO-TABLES with and without trivial calculation detection (base MEMO-TABLE of size 128/4).

access both in the same cycle. Total dynamic instruction count: 11%.

5. Comparison & Conversion - floating point comparisons and conversions from single precision to double precision to integer formats. This table will be smaller (half size) due to the fact that the hit ratios of comparisons and conversions hardly grow with increases in MEMO-TABLE size (section 3.3). Total dynamic instruction count: 12%

Table 3.8 compares using single instruction MEMO-TABLES, multiple instruction MEMO-TABLES and a unified MEMO-TABLE. Using multiple MEMO-TABLES, has the same benefits of using single MEMO-TABLES with a better utilization. Using a unified MEMO-TABLE has a better utilization but can have a higher hit-time which offsets the possible hit-ratio enhancement.

| trait                       | single                  | multiple                  | unified                          |

|-----------------------------|-------------------------|---------------------------|----------------------------------|

| lookup time                 | small table,            | small table,              | larger table,                    |

|                             | low lookup time         | low lookup time           | higher lookup time               |

| table access                | close to FU,            | close to FU,              | distant from some FUs,           |

|                             | uniform access          | uniform access            | nonuniform access                |

| ports                       | read/write              | read/write 1 opcode,      | read/write 1 opcode, 2 operands, |

|                             | 2 operands, 1 result    | 2 operands, 1 result      | 1 result, per FU                 |

| mapping                     | different mapping       | different mapping         | same mapping scheme              |

|                             | schemes                 | schemes                   | for different data types         |

| utilization                 | low, some tables        | moderate, 2-5 instruction | high, all instructions           |

|                             | aren't used             | types per table           | use 1 table                      |

| contention                  | low, only one           | moderate, several         | high, all instructions           |

|                             | instruction per table   | instructions per table    | compete for entries              |

| hardware                    | high, needs comparators | moderate, comparators     | very low, one set                |

| $\operatorname{complexity}$ | and TTU per instruction | and TTU per table         | of comparators and TTU           |

Table 3.8: Comparison of the three MEMO-TABLES contents schemes.

Figure 3.6: hit-ratio of single, multiple, and unified contents scheme. Each MEMO-TABLE is 4-way set associative, uses random replacement, uses the LSBs of the operands (and opcodes) as indices to MEMO-TABLE entries, and performs trivial calculation detection.

Figure 3.6 shows the hit-ratios of 19 single instruction 64 and 128-entry MEMO-TABLES, 5 multiple instruction 256 and 512-entry MEMO-TABLES, and a unified 1024 and 2048-entry MEMO-TABLE. Each level uses approximately the same amount of storage. The rest of the characteristics of the the MEMO-TABLES are 4-way set associativity, random replacement, indexing using the LSBs of the values and opcodes, and trivial calculation detection.

The figure shows the multiple table approach is better than the single table approach and comparable to the unified approach. Given that using multiple MEMO-TABLES is a good compromise between single MEMO-TABLES and a unified MEMO-TABLE (table 3.8), and that the difference in hit-ratios is negligible (figure 3.6) our decision is to use multiple MEMO-TABLES each containing several instruction types.

Using multiple MEMO-TABLES also answers the question: "How does adding MEMO-TABLES impact the die size of the processor?". It is obvious that adding MEMO-TABLES requires additional transistors and wires to bring the operands and results from the FUs to the MEMO-TABLES. However, the size of 5x6KB MEMO-TABLES is 30KB. Modern microprocessors are already integrating L2 caches with sizes in the 256KB range (Intel Pentium-III, AMD Athlon) with future processors projecting onchip caches in the excess of 1MB. In fact, microprocessor designers are looking for beter uses of their transistors than just using them as caches. IM fits this role perfectly. The wire problem is solved by using multiple MEMO-TABLES located adjacent to the FUs that use them, no long, cross chip, wires are needed.

#### 3.5.1 Exploiting Inverse and Commutative Operations

The multiplication, addition, and equality operations are commutative, for example:  $a * b = c \rightarrow b * a = c$ . It might be possible to exploit this trait by performing a *commutative lookup* in the MEMO-TABLE. The index created by hashing the bits of a, b are the same as for b, a. All we have to do now is compare the entries in the set to a, b and to b, a. Thus if a previous instruction calculated

b \* a we will receive a hit for an instruction calculating a \* b. The disadvantage of this technique is that we now need twice the amount of comparators as before. 4-way set associativity becomes 8-way.

Another mathematical rule we can exploit is the properties of inverse operations. If a + b = c were executed and inserted into the Addition MEMO-TABLE, the information to execute operations a = c - b and b = c - a are residing in the MEMO-TABLE. The question is could we exploit this information and memoize instructions that weren't executed even once yet? The same is true for FP multiplication and division. We can't implement the same idea for integers because c/b = a doesn't necessarily imply that a \* b = c (100/3 = 33, 3 \* 33 = 99). The same problem exists for conversions. Converting a FP number to an integer or converting a double precision FP number to a single precision FP number results in loss of accuracy. Therefore trying to perform an inverse lookup can lead to wrong results ( $1.3 \rightarrow 1$  but  $1 \rightarrow 1.0$ ). We built an elaborate mechanism to enable *inverse lookup* and simulated it.

In addition we composed a MEMO-TABLE which we will call the Comparison MEMO-TABLE, which contains the equal, less-then, equal or less-then instructions. In order to have comparisons benefit from previous comparisons between the same two numbers we altered the MEMO-TABLE to store the relationships between two numbers in the result field. It is either -1 (a < b), 0 (a = b), or 1  $(a > b)^9$ .

We ran the benchmarks on this new organization which performs commutative and inverse lookups and stores the relationships between pairs of numbers. The results were disappointing, no increase in the hit-ratio was measured. These new ideas were abandoned in future simulations.

# **3.6 Mapping Strategies**

Until this point in our research we have indexed the MEMO-TABLES using the operand values and specifically the least-significant-bits (LSBs) of the value(s) (XORed them together if a two operand operation is memoized) and used them as an index into a MEMO-TABLE. The benefit of this scheme is it's simplicity and the fact that integer values and FP values can be dealt with in a similar manner. Mapping using the PC was shown to be inferior.

For integer values this mapping strategy is optimal as the LSBs show the highest entropy [23]. For FP numbers this isn't necessarily true. Due to the IEEE 754 representation scheme for FP numbers, where the numbers are normalized, the most-significant-bits (MSBs) of the mantissa or the LSBs of the exponent would seem to be likely candidates for index bits. Another reason not to use the LSBs for FP numbers is in the case where integers are the inputs. In this case the LSBs are all zero, leading to all numbers being mapped to the same entry.

$<sup>^{9}</sup>$ We are assuming that any compare instruction can provide this information, this might not be true for all architectures.

#### 3.6. MAPPING STRATEGIES

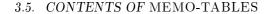

Using these assumptions we devised four additional mapping schemes (assuming the number of sets in a MEMO-TABLE is n):

- Least Significant Bits (lsb) The  $\log_2 n$  LSBs of the mantissa.

- Mantissa (mant) The  $\log_2 n$  most-significant-bits of the mantissa.

- Mixture 1 (mix1) The LSB of the exponent and the  $\log_2 n 1$  MSBs of the mantissa.

- Mixture 2 (mix2) The 2 LSBs of the exponent and the  $\log_2 n 2$  MSBs of the mantissa.

- Exponent (exp) The  $\log_2 n$  least-significant-bits of the exponent.

Figure 3.7 shows the schemes.

Figure 3.7: The index bits are taken from the LSB of the exponent and MSB of the mantissa.

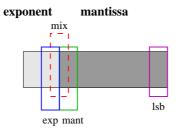

The 5 schemes (and PC indexing) were run on the recommended MEMO-TABLES of section 3.5: multiple MEMO-TABLES of size 256 and 512 and setassociativity of 4. An associativity of 1 and 2 was simulated as well, as a good mapping scheme may result in having to use a lesser degree of associativity. Figure 3.8 shows the hit-ratios of the FP applications (as 4 of the 6 schemes aren't relevant to integer applications).

The graph shows that for a lower associativity the "middle" schemes (mant, mix1, mix2) result in noticeable better hit-ratios. When the associativity is 4 the differences are much smaller with exp, mix1, and mix2 having a slight edge on the lsb and exp schemes. This is due to the flexibility of replacing entries in a set. In a direct-mapped MEMO-TABLE mapping two instructions to the same set results in conflict misses, a better mapping scheme avoids this. If the degree of associativity is higher, instructions mapped to the same set can continue to reside together in the MEMO-TABLE, thus the mapping scheme has less impact.

For any degree of associativity and any size (the results for 512 entry MEMO-TABLES add one percent of hit-ratio to the 256 entry results) using the operand values as indices results in considerable higher hit-ratios than using the PC as an index. The conclusion of this section is that using a mix of bits from the mantissas and exponents of the operand values results in slightly better hitratios than the other operand value schemes and much better hit-ratios than the PC based scheme.

Figure 3.8: hit-ratios of a 256 entry MEMO-TABLE (set associativity 1/2/4) using the 6 mapping schemes

## 3.7 Summary

This chapter investigated the structure of the MEMO-TABLES used in Instruction Memoization (IM). The characteristics of the MEMO-TABLES explored were its size, associativity, replacement method, indexing methods, contents (instruction mix in the MEMO-TABLES) and the detection of trivial calculations.

Our main conclusions from the simulations regarding the organization of MEMO-TABLES are:

- The replacement method is irrelevant, random is as good as LRU.

- A degree of set associativity higher than four is unnecessary.

- Enlarging a MEMO-TABLE beyond a certain point results in diminishing returns as the hit-time increases as well as the hit-ratio.

- Using several MEMO-TABLES for different instruction types enables accessing them concurrently but not having to implement a MEMO-TABLE for every instruction type.

- Inverse and commutative operation lookup is hardly successful and isn't worth the added MEMO-TABLE complexity.

- Using the Program Counter (PC) as the index into a MEMO-TABLE results in much poorer hit-ratios than when the operand values are used as indices.

- By detecting trivial calculations, and not entering the operations into the MEMO-TABLES, a hit-ratio improvement is achieved that is comparable to a four-fold size increase.

Specifically we recommend implementing IM with 5 MEMO-TABLES: (i) for long-latency instructions (FP div, mult, sqrt), (ii) integer instructions (INT div and mult), (iii) FP comparisons and FP $\Leftrightarrow$ INT conversions, (iv) FP addition, (v) and all other FP instructions (sub, neg, ...). Each MEMO-TABLE contains 256 entries in sets of 4 (the Integer MEMO-TABLE's size is 512 and the Comp\_Conv MEMO-TABLE's size is 128). Entries are replaced randomly and are indexed by the 2 LSBs of the exponent and the 6 MSBs of the mantissa XORed with

#### 3.7. SUMMARY

the opcode. Trivial calculations aren't entered into the MEMO-TABLES but are detected with dedicated circuitry. This organization yields an average hit-ratio of 0.50, this is over 80% of the hit-ratio obtained when using an infinite fully-associative MEMO-TABLE (0.60 hit-ratio).

# Chapter 4

# Integrating IM in a Processor's Datapath

This chapter is where we show how IM is integrated into a processor's datapath and enhances execution. We will first integrate multi-cycle instruction memoization (MCIM) in a microprocessor's datapath (section 4.1.4), show the speedup attained (section 4.2), and explore the influence of several datapath characteristics on IM (section 4.3). In the next chapter we will widen the scope of IM to include single-cycle instructions.

### 4.1 A Basic Microprocessor Design

#### 4.1.1 Pipeline Stages

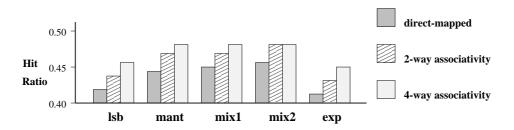

The SimpleScalar simulator, which is modeled after the MIPS series processors, possesses a five stage pipeline for all non Load/Store instructions (figure 4.1):

- 1. Fetch: Instructions are fetched from the Instruction Cache and stored in the Instruction Fetch Queue (IFQ).

- 2. **Decode:** Instructions are read from the IFQ and decoded. Their operand sources are defined: either from the *Register File* (RF) or from instructions that are already in the pipeline. The instructions are entered into the *Register Update Unit* (RUU) (named also the Active List (R10000) or Reorder Buffer (604e)) where they will reside until committed.

- 3. Issue: When an instruction's operands are available it is issued to a free Functional Unit (FU) to be executed, instructions are issued out-of-order. An instruction can be delayed in this stage until it's operand dependencies are satisfied and a FU is available.

- 4. **Execute:** The instruction is executed by one of the FUs (there might be several types and more than one of each type). For multi-cycle instructions

#### 4.1. A BASIC MICROPROCESSOR DESIGN

Figure 4.1: Datapath of basic microprocessor.

this stage takes several cycles. Results are written back into the RUU, where instructions wait to be committed.

5. **Commit:** The instruction is committed by having its result written into the RF and it is removed from the RUU. Instructions are committed in program order, thus even though an instruction has been executed it can't be committed until all previous instructions have been committed.

#### 4.1.2 Functional Units

The processor simulated has five different FU types that execute the processor's instruction set:

- 1. Integer ALU (IALU): Executes all integer instructions (addition, subtraction, logical operations, shifts, comparisons, and branches) with the exception of multiplication and division. All instructions have a latency of one cycle.

- 2. Integer Multiply Unit (IMULT): Executes integer division and multiplication. The unit *may* be pipelined for multiplication, division isn't

## 30 CHAPTER 4. INTEGRATING IM IN A PROCESSOR'S DATAPATH

pipelined.

- 3. Memory Unit (MMU): Executes Load/Stores from the L1 cache.

- 4. Float Add Unit (FADD): Executes floating point addition, subtraction, comparisons, conversions, negations, and absolute value. The unit is pipelined.

- 5. Float Multiplication Unit (FMULT): Executes floating point multiplication, division, and square-root taking. The unit is pipelined only for multiplication.

| L1 Instruction Cache      | 16-KBytes, 32-Byte blocks, direct-mapped         |

|---------------------------|--------------------------------------------------|

| L1 Data Cache             | 16-KBytes, 32-Byte blocks, 4-way associative     |

| L2 Unified Cache          | 256-Kbytes, 64-Byte blocks, 4-way associative    |

| Memory Latencies (cycles) | L1 hit - 1, L2 hit - 6, L2 miss -18              |

| Bus Interface             | 64-bit data, 32-bit address                      |

| Branch Prediction         | 2048-entry BTB, 2-bit counters                   |

| Registers                 | 32 General Purpose, 32 Floating Point            |

| Function Units            | 2 IALU, 1 IMULT                                  |

|                           | 1 FADD unit, 1 FMULT, 2 MMU                      |

| Instruction Latencies     | Integer multiplication: 4,1                      |

| & Throughputs             | Integer division: 20,19                          |

|                           | All other integer instructions: 1,1              |

|                           | Floating point multiplication: 3,1               |

|                           | Floating point division: 20,20                   |

|                           | Floating point Sqrt: 35,35                       |

|                           | All other floating point instructions: 2,1       |

| Pipeline attributes       | 4-instructions fetched, decoded, issued,         |

|                           | and committed per cycle; 16 instructions in RUU, |

|                           | out-of-order execution, in-order retirement      |

## 4.1.3 **Processor Characteristics**

Table 4.1: Characteristics of basic microprocessor.

The characteristics of the basic datapath we used in our first set of simulations is listed in table 4.1. This processor is called the *basic* processor. It's characteristic values where taken from two popular RISC processors, the MIPS R10000 [24] and PPC 604e [25], and from the default values of the SimpleScalar simulator.

## 4.1.4 Integrating IM

The 5 MEMO-TABLES described in the previous chapter are integrated adjacent to the relevant FUs (figure 4.2). The questions we are confronted with are: At what stage in the pipeline is memoization performed? What is the latency of

## 4.1. A BASIC MICROPROCESSOR DESIGN

Figure 4.2: Integration of IM in the datapath.

a MEMO-TABLE lookup? How many lookups per cycle can a MEMO-TABLE sustain? We will answer the questions in the following sections.

## **Pipeline Stage**

As the instruction's operands must be ready before memoization may commence there are three alternatives:

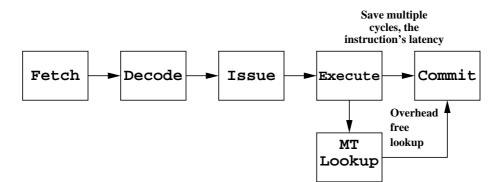

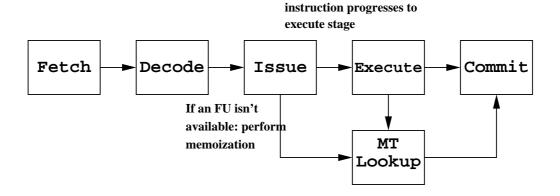

• Execute stage: After the instruction is allocated to a FU the MEMO-TABLE lookup and instruction execution are performed in parallel. A hit terminates the execution, a miss results in the completion of execution and updating the MEMO-TABLE with the result. Successful lookups complete in 1 cycle, unsuccessful lookups complete in the latency of the instruction.

#### 32 CHAPTER 4. INTEGRATING IM IN A PROCESSOR'S DATAPATH

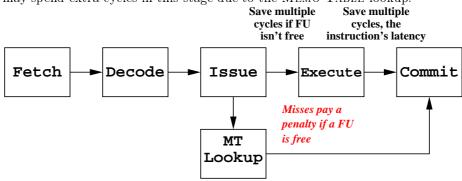

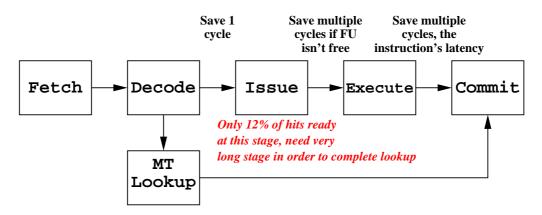

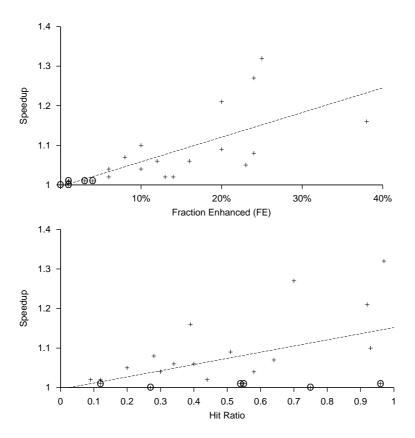

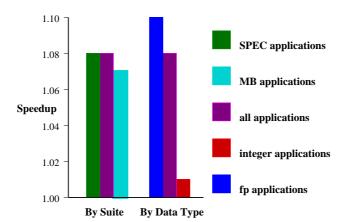

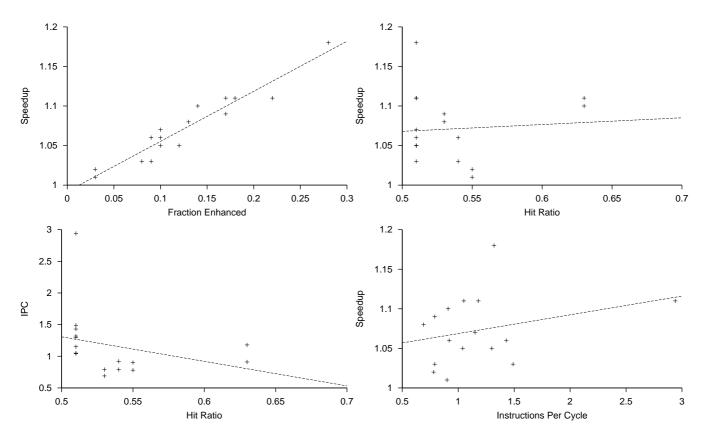

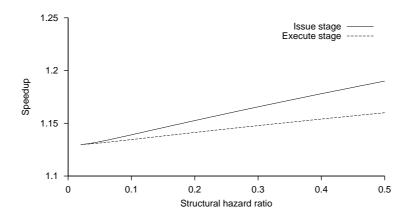

• Issue stage: When the operands are ready we perform a MEMO-TABLE lookup, whether a FU is ready or not. A hit results in the instruction bypassing the execute stage, a miss results in the instruction waiting for a FU, executing, and updating the MEMO-TABLE. Successful lookups complete in 1 cycle and may gain cycles if a FU isn't available. Unsuccessful lookups lose one cycle due to the lookup, wait for a FU to be available, and then complete in the latency of the instruction. Thus an instruction may spend extra cycles in this stage due to the MEMO-TABLE lookup.